## **FINAL 1:**

- 1) Escribir una rutina ARC que reciba a través de la pila dos valores enteros en complemento a 2 de 32 bits y luego verifique si la suma de ambos no excede el rango representable. Si este rango no es excedido termina sin devolver parámetros. En caso contrario completa con ceros las 12 palabras siguientes a la dirección 3000 (decimal) y a continuación termina.

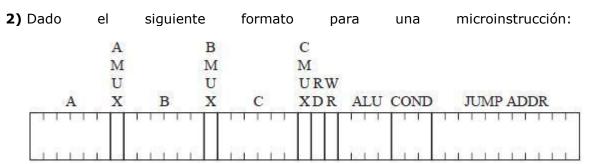

- Durante la ejecución de un microprograma las sucesivas microinstrucciones van siendo cargadas en el MIR. Explique la lógica digital que define la dirección de la microinstrucción a ser cargada.

- 3) El trayecto de datos incluye tanto multiplexores como decodificadores, explique las características y función desempeñada por cada uno de los decodificadores y por cada uno de los multiplexores.

- 4) Un procesador accede a memoria por datos de 8 bits y posee 16 bits para direccionarlos. Diseñar un sistema tal que puedan almacenarse datos en los primeros 8 Kbytes y en los últimos 32 Kbytes.

- Para ello se cuenta con memorias de 4 K posiciones de 1 bit y memorias de 16 K posiciones de 8 bits. En ambas la entrada de habilitación se activa con nivel bajo.

- -Dar las ecuaciones algebraicas de las entradas de habilitación

- -Presentar el circuito de la lógica de decodificación haciendo uso de decodificadores, indicando

- claramente todas las conexiones con el procesador.

- Realice un comentario tan extenso como considere necesario respecto de la veracidad o no de las siguientes afirmaciones (tome cada una en forma independiente del resto)

- d) "La existencia del cache es transparente al programador"

- e) "El aprovechamiento del cache es optimo si el programa maneja muchas variables en memoria"

- f) "Un procesador con cache podría ser mas lento que otro sin cache en determinadas condiciones"

#### FINAL 2

- Escribir una rutina ARC que reciba a través de la pila dos valores enteros en complemento a 2 de 32 bits y luego verifique si la suma de ambos no excede el rango representable. Si este rango no es excedido termina sin devolver parámetros. En caso contrario completa con ceros las 12 palabras siguientes a la dirección 3000 (decimal) y a continuación termina.

- Durante la ejecución de un microprograma las sucesivas microinstrucciones van siendo cargadas en el MIR. Explique la lógica digital que define la dirección de la microinstrucción a ser cargada.

- 3) El trayecto de datos incluye tanto multiplexores como decodificadores, explique las características y función desempeñada por cada uno de los decodificadores y por cada uno de los multiplexores.

- 4) Un procesador accede a memoria por datos de 8 bits y posee 16 bits para direccionarlos. Diseñar un sistema tal que puedan almacenarse datos en los primeros 8 Kbytes y en los últimos 32 Kbytes.

- Para ello se cuenta con memorias de 4 K posiciones de 1 bit y memorias de 16 K posiciones de 8 bits. En ambas la entrada de habilitación se activa con nivel bajo.

- -Dar las ecuaciones algebraicas de las entradas de habilitación

- -Presentar el circuito de la lógica de decodificación haciendo uso de decodificadores, indicando

- claramente todas las conexiones con el procesador.

- Realice un comentario tan extenso como considere necesario respecto de la veracidad o no de las siguientes afirmaciones (tome cada una en forma independiente del resto)

- d) "La existencia del cache es transparente al programador"

- e) "El aprovechamiento del cache es optimo si el programa maneja muchas variables en memoria"

- f) "Un procesador con cache podría ser mas lento que otro sin cache en determinadas condiciones"

### FINAL 3

- 1) Un programa ARC declara dos vectores de 15 elementos cada uno (enteros con signo) e invoca una rutina que se encarga de sumar ambos vectores. La rutina recibe como parámetros las direcciones de inicio de cada sumando, su largo, y la dirección de inicio del vector resultado. Si al realizar la suma ocurre una condición de fuera de rango la rutina devuelve un 1 y si la suma se realizó con éxito devuelve un 0. En cualquier caso se completa la suma de todos los elementos homólogos. La rutina y el programa principal deben definirse en módulos separados. El pasaje de parámetros será vía stack. El vector resultado debe sobrescribir el primero de los vectores sumando.

- Indique todas las directivas al ensamblador que considere apropiadas.

- 2) Indique tabla de símbolos correspondiente al código del punto 1. Explique de qué manera esa información es procesada por el linker y por el loader.

- 3) La instrucción ARC andcc es decodificada por medio de la siguiente secuencia de microinstrucciones

```

1604: IF R[IR[13]] THEN GOTO 1606;

1605: R[rd] = ANDCC(R[rs1],R[rs2]);

GOTO 2047;

1606: R[temp0] = SIMM13(R[ir]);

1607: R[rd] = ANDCC(R[rs1],R[temp0]);

GOTO 2047;

```

- a) Realizar un diagrama completo de la microarquitectura ARC microprogramada.

- b) Explicar de qué manera intervienen cada uno de los componentes presentados en el punto (a) durante la tarea de decodificar la instrucción andcc %r1, FFh, \$r3 Indicar como se llega al inicio de esa microrutina y como se ejecutan en hardware cada uno de sus pasos (indicar valores en entradas y salidas de registros, decodificadores, multiplexores, etc.).

- c) Describir de qué manera la ejecución continúa hacia la siguiente instrucción Assembly.

- 4) Presente un posible diagrama circuital para el registro %r20 basándose en flipflops tipo D sensibles a flanco descendente. Incluya todas las conexiones con los buses de datos, address y control.

# FINAL 4

- Proponga un programa Assembler ARC que realice la suma de los valores almacenados entre las direcciones 1F652702h y 1F652720h. Esta suma es obtenida por una subrutina que recibe via stack ambas direcciones. El resultado de esta suma es devuelto por la subrutina también via stack.

- 2) Indique si considera que el procesador ARC es de tipo CISC o RISC. Compare ambas tipo arquitectura.

- 3) Explique qué entiende por ciclo de búsqueda-ejecución (ciclo de fetch). Explique el modo por el cual este es implementado a través del firmware de una microarquitectura ARC. Detalle el microcódigo asociado.

- 4) Indique la función de las señales RAS Y CAS en un modulo de memoria DIMM.

- 5) Indique el contenido binario de la memoria de control que corresponder al siguiente microcódigo:

```

1627: R[rd] <-- NORCC(R[rs1],R[temp0]);

GOTO 2047;

```

### Final 5

1) Se tiene un banco de memoria de 64K palabras de 16 bits, se pide conectar el bus de address y de datos para conseguir que esten disponibles con memoria RAM los 16K superiores, y los 2K inferiores. Para realizar el ejercicio se cuenta con chips de memoria de 8KB,4KB y 2KB en cantidades suficientes. Realizar todas las conexiones, y escribir la función algebraica de los Chips Select (CS).

Se pide dar una posible conexión con el camino de datos (Datapath)

**3)** Explicar el concepto de bus, cuales son sus ventajas. Explicar que es Bus de sistema, y compararlo con el modelo Von Neumann.

**4)** *a)* Se tienen las siguientes instrucciones:

```

PUSH arg1 // envía el contenido de arg1 a la pila

POP arg1 // baja lo que haya en la última posición de la pila

// al contenido de arg1

ADD arg1,arg2,arg3 // arg1 <- arg2 + arg3

```

Explicar cuál es el resultado del siguiente fragmento de código, siendo A y B direcciones de memoria: (Aclaración del profesor: ADD A,1,A suma 1 al contenido de A, no a su dirección)

PUSH A

ADD A,1,A

PUSH A

ADD A,1,A

PUSH A

POP B

ADD B,-1,B

POP B

ADD B,-1,B

POP B

b) Explicar qué ventajas podría tener el uso del Stack, y dar ejemplo de en qué métodos me conviene usarlo.