66.20 Organización de Computadoras - Segundo Parcial

Práctica: Jueves

23 de noviembre de 2006

- Principios Cuantitativos de Diseño Un benchmark dado contiene 195578 operaciones de punto flotante, con el siguiente detalle: \\El benchmark se ejecutó en un procesador empotrado. El mismo está basado en un diseño RISC que incluye lógica para punto flotante, pero el procesador empotrado no la incluye por cuestiones de costo. El compilador permite que las instrucciones de punto flotante se resuelvan con la lógica de punto flotante (si se dispone de ella) o emuiladas por software. El benchmark tardó 1,08 segundos en el procesdador RISC, y 13,6 segundos usando la emulación por software en el empotrado. El CPI promedio medido en el RISC es de 10 siclos por instricción, mientras que para el empotrado es de 6 ciclos por instrucción. En ambos casos, la frecuencia de reloj es de 10 Mhz. (Ver tabla al final del documento).

- ¿Cúal es la cantidad total de instrucciones ejecutadas en ambos casos (RISC y empotrado)?

- ¿Cuál es la tasa de MIPS para ambos casos (RISC y empotrado)?

- En promedio, ¿cúantas instrucciones de enteros insume una operación de punto flotante, cuando es emulada por software?

- En base a la tasa de MIPS ¿qué procesador prefiere?¿Y en base a los tiempos de ejecución?. Justifique.

- ¿Cuál es sería el speedup alcanzado si se le incorpora la lógica de punto flotante al empotrado?

- Programación Assembly

Dado el siguiente programa en lenguaje C:

int suma (int a, int b, int c, int, d, int *r){ *r = a + b + c + d; return *r;\\ } int main(void){ int r; suma(1,2,3,4,&r); return 0; }

Escribirlo usando assembly de MIPS32, respetando a rajatabla la convención estudiada en el curso (no la del trabajo práctico), y en no más de 50 líneas de código. El código generado no debe estar optimizado, y debe respetar el hecho de que esta es una arquitectura de carga-almacenamiento. Dibujar los stack frames. 1)

- Sistema de Memoria

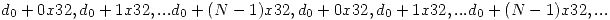

Se dispone de una organización caché L1 de datos de caractéristicas desconocidas (solo se sabe que el tamaña del bloque es de 32 bytes y que la política de remplazo es LRU). Se ejecuta un benchmark que referencia, en forma cíclica, a un conjunto de N bloques consecutivos partiendo de la dirección d0 (al terminar de “barrer” los N bloques consecutivos, vuelve a comenzar con el primero, y así infinitamente), como se muestra a continuación:

El benchmark se ejecuta, por un tiemop muy extenso (tal que son despreciables los desaciertos por warm-up), para diferentes valores de N (tamaño del “lazo”) y, en cada ejecución, se mide la cantidad de desaciertos producidos en la memoria en cuestión. Esos datos se expresan en el siguiente gráfico:

Indicar el tamaño total y la cantidad de vías de la memoria caché.

Tabla del Ej 1:

| Operración | Cantidad |

|---|---|

| Suma | 82014 |

| Resta | 8229 |

| Multiplicación | 73220 |

| División | 21399 |

| Conversión entero → punto flotante | 82014 |

| Comparacíon | 4710 |

| Total | 195578 |

1)

Con el enunciado daban el Conjunto de Instrucciones de Assembly para MIPS32

Excepto donde se indique lo contrario, el contenido de esta wiki se autoriza bajo la siguiente licencia: CC Attribution-Noncommercial-Share Alike 3.0 Unported